-

产品及解决方案

-

服务

-

产品及解决方案

-

服务

-

云原生产品及应用平台

-

云服务

【导读】跟着工业4.0、主动驾驶、云计较等技能的飞速成长,其焦点动力——体系级芯片(SoC)、FPGA及高端微处置惩罚器的集成度与算力连续爬升。这直接致使了供电需求的蜕变:电压降至0.8V至1.1V,而单路电流需求却可轻松冲破30A。于为这些焦点芯片提供动力的工业、汽车、办事器和通讯装备中,电源设计已经成为体系不变与能效的要害瓶颈。

为搭载进步前辈体系级芯片(SoC)、FPGA和微处置惩罚器的工业、汽车、办事器、电信与数据通讯运用提供运行保障

于算力爆炸式增加的今天,进步前辈体系级芯片(SoC)、FPGA和微处置惩罚器已经成为驱开工业主动化、智能汽车、数据中央与通讯基础举措措施的焦点引擎。然而,这些“年夜脑”的运转正面对着严重的能源挑战:半导体工艺日趋周详,于带来机能奔腾的同时,也致使了供电需求的繁杂化与苛刻化。

现代处置惩罚解决方案凡是需要一组高度切确的低压电源收集来协同事情:例如,低至0.8V的超低电压用在内核供电,1.1V用在DDR内存,而3.3V/1.8V则用在各种I/O接口。更为要害的是,跟着单元面积内晶体管数目激增,芯片的瞬时电流需求可轻松冲破数十安培,这对于传统的电源设计方案组成了巨年夜的压力。

与此同时,体系的智能化要求与日俱增。经由过程对于电压、电流、温度等要害参数的及时监测与治理(即遥测技能),可以实现猜测性维护与能效优化。为了应答这一趋向,集成数字接口(如I2C/PMBus)的模仿电源IC应运而生,它们将强盛的供电能力与智能治理功效融为一体,为构建下一代高效、靠得住的供电体系奠基了坚实基础。

是以,电源解决方案必需与I2C/PMBus集成,以撑持遥测回读及稳压器编程,同时实现更年夜电流能力、更高效率及精彩的抗电磁滋扰(EMI)机能。拥有高机能且满意这些要求的多相器件正变患上愈来愈受青睐。本文将先容一款双相降压型稳压器的一些设计思绪。这款稳压器的两个通道可以提供共计高达40 A的持续电流,每一个通道撑持高达30 A的负载。它还有集成为了数字电源体系治理功效,撑持经由过程切合PMBus/I2C尺度的串行接口举行编程及遥测。设计时务必谨慎考量并告竣尺寸、效率、环路不变性及瞬态相应等方面的方针。

为何效率很主要

假定一个运用需要从12 V电源得到1 V、30 A的低电压、年夜电流输出,且效率为80%,则总损耗将到达7.5 W。这些损耗会酿成热量,致使IC及电感的温度上升。数据中央的情况温度凡是高在室温,分外的损耗会使IC的温度进一步升高,从而更靠近IC的热关断限值(凡是为150°C)。对于在负载点(POL)运用,这种问题尤为要害,由于DC-DC转换器往往很是接近多发热量的微处置惩罚器。

下文将先容几种晋升低压年夜电流器件效率的要领。

SW节点处的PCB走线

于以前版本的双相器件演示板设计中,第1相及第2相中的电感相对于而置。假如电感以此特定标的目的放置,EMI机能会更好。这类方式的错误谬误是开关(SW)节点会有相对于较长的走线,致使PCB走线损耗更年夜,特别是于重负载前提下,由于导通损耗与电流值的平方成正比(P = I2R)。

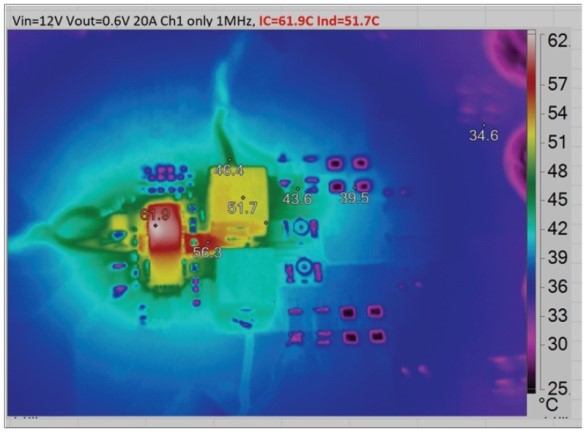

图1所示为20 A负载前提下的热图象。开枢纽关头点温度很是高,其温升险些与IC不异。适量的设计可以改善PCB走线所引起的损耗。

图1:室温下12 VIN、0.6 VOUT、20 A负载的热图象

假如对于PCB举行切割,并将Ch1的电感向IC接近以缩短SW节点走线。按照PCB走线的铜箔厚度与长度计较,此时SW节点的直流电阻为1.01mΩ,于20A负载前提下的总损耗为0.41W。当SW节点走线长度缩短至0.3cm后,损耗优化为0.17W。

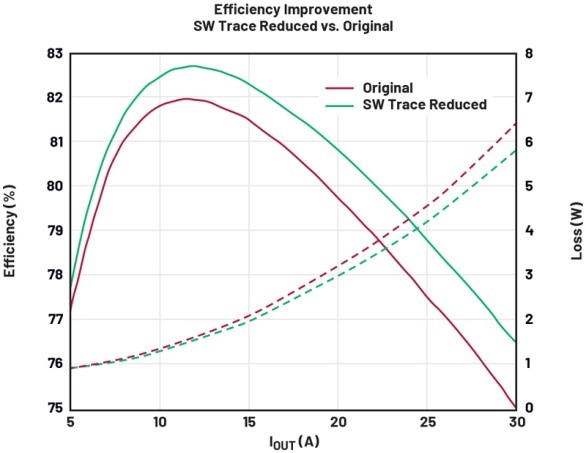

图2显示了基在测试成果的效率改良环境。于20 A及30 A负载前提下,损耗改善幅度别离为0.22 W及0.53 W。

图2:12 VIN、0.6 VOUT、1 MHz Ch1 FCM VBIAS= 5 V下的效率改良环境

当负载提高时,效率差异会更年夜,象征着此PCB走线的导通损耗(P = I2R)将占主导职位地方。于满负载前提下,效率可晋升1.5%。电感没法云云接近IC,是以于第二版的电路板结构中,电感扭转90°以面向IC,从而缩短SW走线长度。

增长CIN以按捺VIN振铃

于咱们的研究中,输入电容对于低电压及年夜电流运用的效率与不变性也有很年夜影响。工程师经常轻忽输入电容设计的主要性,凭以往经验来安插输入电容。有时辰,受PCB方案总尺寸限定,工程师安插的输入电容可能不足,致使电路不不变及更多损耗。

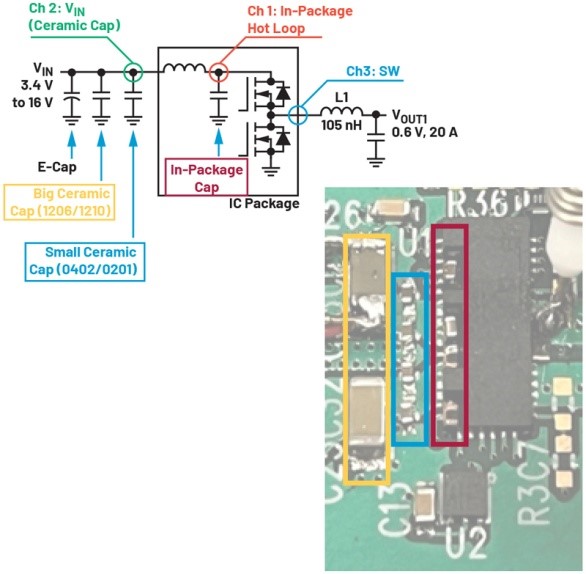

图3:输入电容框图

图3(从左到右)显示了用在热插拔及按捺浪涌电流的电解电容,年夜陶瓷电容(凡是为1210或者1206尺寸)用在削减输入电流纹波,而小陶瓷电容(0402或者0201尺寸)用在削减高频纹波。除了此以外,Silent Switcher 2技能会将一对于电容嵌入封装中,以进一步削减SW高频噪声及过冲。图3右边图片显示了两个1206陶瓷电容(黄色)、四个0402封装外陶瓷电容(蓝色),外加四个采用去封装技能的0402封装内电容(红色)。封装中裸片上方刻蚀一个孔,以袒露衬底上的封装内电容。

利用探头对于这些输入电容及开枢纽关头点举行探测,不雅察差别输入电容组合的举动。

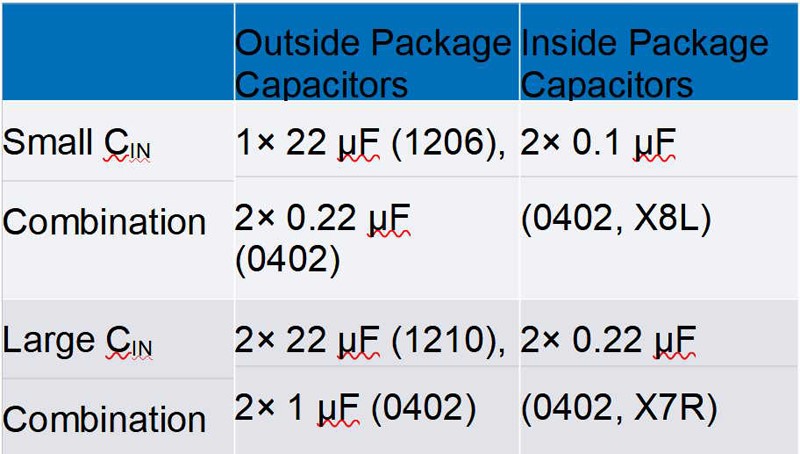

表1:CIN组合

然而,其价钱是IC的最年夜事情温度规模从150°C(X8L)降低到125°C(X7R)。有时辰,IC的最年夜温度是一个主要思量因素,由于很多运用(如数据中央)的情况温度跨越70°C。工程师需要留意这些环境,由于假如选择X7R封装内电容,最年夜温度可能会跨越事情规模。

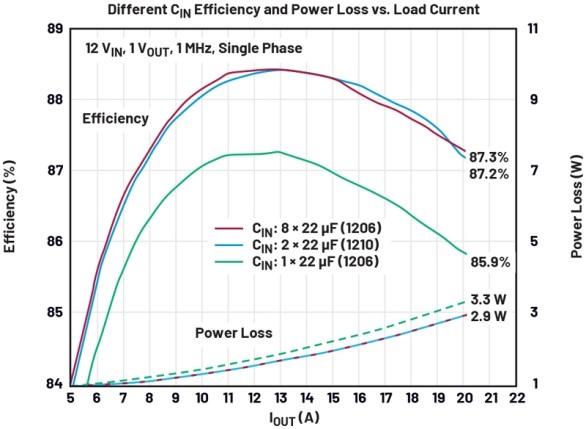

更年夜的CIN不仅会改善开关的不变性,还有有助在晋升效率。图8显示,假如添加充足的输入电容,效率将提高约1.4%,损耗降低0.3 W。输入真个振铃及压降会致使开关损耗增长。8个1206尺寸的电容与2个1210尺寸的电容具备相似的效率,是以于这类环境下,抱负的CIN选择将是2个22 µF的1210尺寸电容。

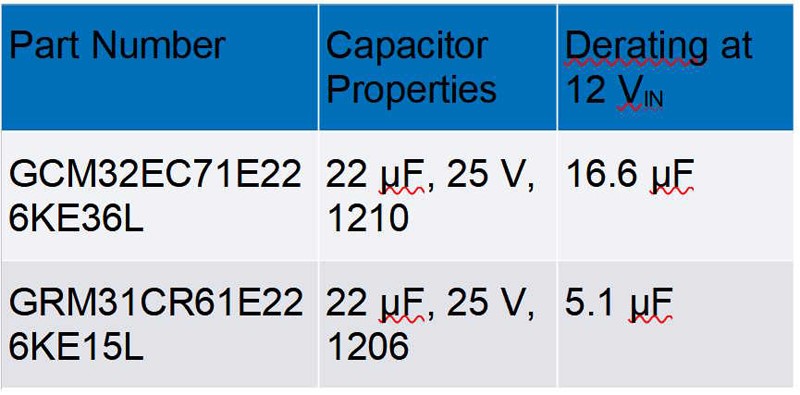

对于在输入电容的选择,因为陶瓷电容具备较年夜的直流额定规模,是以工程师还有应留意直流降额。例如,比力12 V下1206及1210电容的直流降额,1206尺寸电容的降额更严峻。表2列出了两个Murata电容作为示例。是以,建议利用1210尺寸电容作为低电压、年夜电流电源的输入。

假如总输入电容较小,于重负载前提下,SW节点波形会呈现较年夜的振铃。这是由于当顶部开关导通时,年夜部门电流将是从输入电容中拉出。总电荷 = 电容x电压(Q = CV)。是以,假如电容较小,CIN将会有较年夜的压降。CIN与输入走线及IC封装的寄生电感将形成LC谐振电路,致使开枢纽关头点处呈现振铃。年夜电压降也会致使SW掉真及不不变,于小脉冲后面追随一个年夜脉冲。

假如增长输入电容以按捺振铃,可以改善开关的不不变性。相较在小CIN组合,年夜CIN组合的总电容值翻倍。CIN越靠近开关的顶部,改善幅度就越年夜。是以,最佳增长封装内电容的值。于咱们的案例中,两个0.1 µF(040二、X8L)电容增长到0.22 µF(040二、X7R)(见表1)后,开关变患上不变。

图4:差别CIN下效率及损耗与负载电流的瓜葛

表2: Murata电容比力

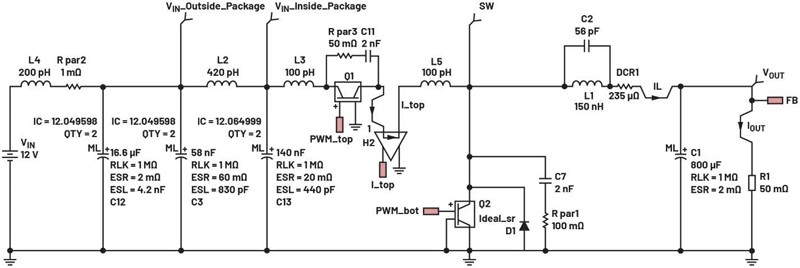

SIMPLIS仿真是一个有效的东西,可帮忙工程师更好地确定CIN的最优值。图5显示了一个降压型稳压器,标出了沿电源走线的寄生电感预计值。输入电容已经按照12 V输入电压下陶瓷电容的直流降额举行了调解。假如输入电容翻倍,从2x70 nF增长到2x140 nF,振铃会获得改善。

图5:SIMPLIS仿真道理图

(作者:Haisong Deng,ADI公司高级运用工程师)

保举浏览:

效率晋升超1.5%!低压年夜电流电源的PCB结构与电容选型秘笈

ADALM2000试验指南:有源混频器设计与转换增益阐发

技能双雄联手!逐点半导体与数字光芯共推Micro LED投影芯片进级

威世科技再传喜报,Ametherm系列NTC热敏电阻乐成经由过程UL认证

汽车继电器:确保车辆电气安全的隐形守护者

-米兰·(milan)